Copper-silicide

Description

BenchChem offers high-quality Copper-silicide suitable for many research applications. Different packaging options are available to accommodate customers' requirements. Please inquire for more information about Copper-silicide including the price, delivery time, and more detailed information at info@benchchem.com.

Properties

Molecular Formula |

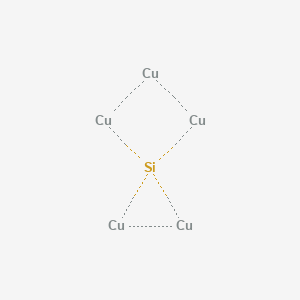

Cu5Si |

|---|---|

Molecular Weight |

345.81 g/mol |

InChI |

InChI=1S/5Cu.Si |

InChI Key |

JUZTWRXHHZRLED-UHFFFAOYSA-N |

Canonical SMILES |

[Si].[Cu].[Cu].[Cu].[Cu].[Cu] |

Origin of Product |

United States |

Foundational & Exploratory

Unveiling the Atomic Architecture: A Technical Guide to the Crystal Structures of Copper Silicide Phases

An in-depth exploration of the crystallographic properties of various copper silicide phases, providing researchers, scientists, and material development professionals with a comprehensive understanding of their atomic arrangements and the experimental techniques used for their characterization.

Copper silicides are a fascinating class of intermetallic compounds with significant technological importance, finding applications in areas ranging from microelectronics to catalysis. A thorough understanding of their crystal structures is paramount for predicting and controlling their physical and chemical properties. This technical guide provides a detailed overview of the crystal structures of prominent copper silicide phases, including the polymorphic forms of Cu₃Si, as well as Cu₅Si and Cu₁₅Si₄. Furthermore, it outlines the key experimental protocols for their structural determination using X-ray diffraction (XRD) and transmission electron microscopy (TEM).

Crystal Structure Data of Copper Silicide Phases

The arrangement of copper and silicon atoms in the crystal lattice defines the specific phase of copper silicide and dictates its material properties. The following tables summarize the key crystallographic data for several known copper silicide phases.

Table 1: Crystal Structure Data for Cu₃Si Polymorphs

| Phase Name | Common Name(s) | Crystal System | Space Group | Lattice Parameters (Å) |

| η-Cu₃Si | High-Temperature Phase | Trigonal | R-3m (No. 166) | a = 4.04, c = 2.44 |

| η'-Cu₃Si | Intermediate-Temperature Phase | Trigonal | R-3 (No. 148) | a = 7.00, c = 7.33 |

| η''-Cu₃Si | Low-Temperature Phase | Orthorhombic | Cmc2₁ (No. 36) or other complex superstructures have been proposed. | a ≈ 7.68, b ≈ 7.00, c ≈ 21.94 (superlattice) |

Table 2: Crystal Structure Data for Other Copper Silicide Phases

| Phase Name | Common Name(s) | Crystal System | Space Group | Lattice Parameters (Å) |

| γ-Cu₅Si | Cubic | P4₁32 (No. 213) | a = 6.222 | |

| ε-Cu₁₅Si₄ | Cubic | I-43d (No. 220) | a = 9.712 |

Experimental Protocols for Crystal Structure Determination

The precise determination of the crystal structures of copper silicide phases relies on sophisticated experimental techniques. The two primary methods employed are X-ray Diffraction (XRD) and Transmission Electron Microscopy (TEM).

X-ray Diffraction (XRD) Analysis

XRD is a powerful non-destructive technique used to identify the crystalline phases present in a material and to determine their crystal structures.

Powder XRD is suitable for the analysis of bulk polycrystalline copper silicide samples.

-

Sample Preparation:

-

Grind the bulk copper silicide sample into a fine, homogeneous powder using a mortar and pestle. The particle size should ideally be less than 10 µm to ensure good particle statistics and minimize preferred orientation effects.

-

Mount the powder onto a sample holder. A zero-background sample holder is recommended to minimize background noise in the diffraction pattern. Ensure the sample surface is flat and level with the surface of the holder.

-

-

Data Collection:

-

Use a powder diffractometer equipped with a monochromatic X-ray source (e.g., Cu Kα radiation, λ = 1.5406 Å).

-

Set the appropriate instrument parameters, including the voltage and current for the X-ray tube (e.g., 40 kV and 40 mA).

-

Scan a wide 2θ range (e.g., 20° to 100°) with a small step size (e.g., 0.02°) and a sufficient counting time per step to obtain a high-quality diffraction pattern with good signal-to-noise ratio.

-

-

Data Analysis:

-

Perform phase identification by comparing the experimental diffraction pattern to standard diffraction patterns in a database such as the Powder Diffraction File (PDF) from the International Centre for Diffraction Data (ICDD).

-

For detailed crystal structure analysis, perform Rietveld refinement of the powder diffraction data. This involves fitting a calculated diffraction pattern, based on a structural model, to the experimental data. The refinement process optimizes various parameters, including lattice parameters, atomic positions, and site occupancies, to achieve the best possible fit.[1]

-

For thin films of copper silicide, GIXRD is employed to enhance the signal from the film while minimizing the signal from the substrate.[2][3]

-

Sample Alignment:

-

Mount the thin-film sample on the diffractometer stage.

-

Carefully align the sample to ensure the incident X-ray beam strikes the surface at a very small, fixed angle (the grazing angle), typically between 0.5° and 2°.

-

-

Data Collection:

-

Use a diffractometer configured for parallel beam geometry.

-

Select an appropriate grazing angle of incidence. A smaller angle increases surface sensitivity but may decrease the overall signal intensity.

-

Scan the detector over a desired 2θ range to collect the diffraction pattern from the thin film.

-

-

Data Analysis:

-

Identify the crystalline phases present in the thin film by comparing the GIXRD pattern to reference data.

-

Analyze the peak positions to determine the lattice parameters of the thin film.

-

Analyze peak broadening to estimate crystallite size and microstrain within the film.

-

Transmission Electron Microscopy (TEM) Analysis

TEM provides direct imaging of the crystal structure at the nanoscale and can be used to obtain electron diffraction patterns from very small volumes of material.

XTEM is ideal for examining the crystal structure of thin films and interfaces.[4][5]

-

Protective Layer Deposition: Deposit a protective layer (e.g., platinum or carbon) onto the area of interest on the sample surface to prevent damage during ion milling.

-

Trench Milling: Use a high-current gallium ion beam in the FIB to mill two trenches on either side of the region of interest, creating a thin lamella.

-

Lamella Extraction: Carefully cut the lamella free from the bulk sample using the ion beam and lift it out using a micromanipulator.

-

Mounting: Transfer the lamella to a TEM grid and weld it in place using ion-beam-induced deposition.

-

Final Thinning: Use a low-current ion beam to thin the lamella to electron transparency (typically < 100 nm). A final low-energy milling step can be used to remove any amorphous layers created during the higher-energy milling.

PV-TEM allows for the examination of the crystal structure parallel to the film surface.

-

Backside Thinning: Mechanically polish and dimple the substrate from the backside to a thickness of a few tens of micrometers.

-

Ion Milling: Use a broad-beam argon ion mill to thin the sample from the backside until a small hole is created in the substrate, leaving an electron-transparent region of the thin film around the edge of the hole.

-

Final Cleaning: A low-energy ion milling step can be used to clean the surface of the thin film.

Visualizing Relationships and Workflows

Diagrams are essential for visualizing the relationships between different phases and the experimental procedures used to study them.

References

- 1. MyScope [myscope.training]

- 2. physlab.org [physlab.org]

- 3. Grazing Incidence X-Ray Diffraction (GIXRD) | Malvern Panalytical [malvernpanalytical.com]

- 4. Cross-sectional sample preparation by focused ion beam: a review of ion-sample interaction - PubMed [pubmed.ncbi.nlm.nih.gov]

- 5. academic.oup.com [academic.oup.com]

Intermetallic Phases and Solid Solutions

An In-depth Technical Guide to the Copper-Silicon Phase Diagram

The copper-silicon (Cu-Si) system is of significant industrial and scientific interest, forming the basis for silicon bronzes and playing a crucial role in microelectronics. The binary phase diagram of this system is characterized by a series of intermetallic compounds and complex invariant reactions.[1][2] This guide provides a detailed explanation of the Cu-Si phase equilibria, summarizing the quantitative data, outlining experimental determination protocols, and visualizing key transformations.

The Cu-Si system consists of terminal solid solutions, (Cu) and (Si), and several intermediate phases. The copper-rich side of the diagram is particularly complex, featuring numerous intermetallic compounds.[1][3] Many of these phases, such as β and δ, are only stable at high temperatures and cannot be retained by quenching.[4][5] The η phase (Cu3Si) is notable for its polymorphic nature, existing in three different modifications: η, η', and η''.[1][6]

Table 1: Crystal Structure and Composition of Phases in the Cu-Si System

| Phase | Composition (at.% Si) | Pearson Symbol | Crystal System | Space Group | Notes |

|---|---|---|---|---|---|

| (Cu) | 0 - 11 | cF4 | Cubic | Fm-3m | FCC solid solution of Si in Cu.[3] |

| β | 14.3 - 16.5 | cI2 | Cubic | Im-3m | High-temperature bcc phase.[3][4] |

| γ | 22.7 - 26.3 | hR* | Rhombohedral | R-3m | [3] |

| γ' | 24.1 - 26.3 | hR* | Rhombohedral | R-3 | Intermediate temperature modification.[3][6] |

| γ'' (η'') | 24.3 - 26.3 | o** | Orthorhombic | - | Low-temperature modification of Cu3Si.[3][6] |

| δ | 17 - 18 | cP20 | Cubic | P4₁32 | βMn prototype structure.[3] |

| ε | ~21.2 (Cu₁₅Si₄) | cI176 | Cubic | I-43d | Stability is debated; may be kinetically inhibited.[1][4][5] |

| η | 24.1 - 26.3 | hR* | Rhombohedral | R-3m | High-temperature modification of Cu3Si.[1][6] |

| η' | 24.1 - 26.3 | hR* | Rhombohedral | R-3 | Intermediate temperature modification of Cu3Si.[1][6] |

| (Si) | ~100 | cF8 | Cubic | Fd-3m | Diamond cubic solid solution of Cu in Si.[3] |

Note: The nomenclature for the polymorphic forms of Cu₃Si (γ and η) can be inconsistent in literature. This table reflects common designations.[1][3]

Invariant Reactions

The transformations within the Cu-Si system are governed by several invariant reactions, where three phases are in equilibrium at a specific temperature and composition. These include eutectic, peritectic, eutectoid, and peritectoid reactions.[7][8][9][10]

Table 2: Key Invariant Reactions in the Cu-Si System

| Reaction Type | Temperature (°C) | Approx. Composition (at.% Si) | Reaction Equation |

|---|---|---|---|

| Peritectic | 1023 | ~11 | L + (Cu) ↔ β |

| Peritectic | 842 | ~15 | L + β ↔ κ |

| Eutectic | 802.5 | 12.1 | L ↔ (Cu) + κ |

| Eutectoid | 780 | ~12 | κ ↔ (Cu) + γ |

| Congruent Melting | 859 | 25 | L ↔ η |

| Peritectoid | 735 | ~17.5 | β + δ ↔ γ |

| Eutectoid | 710 | ~16 | β ↔ (Cu) + γ |

| Eutectoid | 552 | ~12.5 | κ ↔ (Cu) + η'' |

Data synthesized from multiple sources, precise values may vary slightly between assessments.[1][11]

Figure 1: Visualization of key invariant solid-state reactions.

Experimental Determination Protocols

The determination of the Cu-Si phase diagram is accomplished through a combination of experimental techniques designed to identify phase transition temperatures, crystal structures, and compositions.[1][4]

1. Sample Preparation and Synthesis:

-

Alloy Preparation: High-purity copper and silicon are weighed to precise compositions and melted together, often using induction melting in a vacuum or inert atmosphere to prevent oxidation.[6] Alternatively, powder metallurgy techniques can be employed.[12]

-

Homogenization: The resulting alloys are annealed at elevated temperatures for extended periods (e.g., 24 hours or more) to ensure a uniform chemical composition and achieve thermodynamic equilibrium.[6]

2. Thermal Analysis:

-

Differential Thermal Analysis (DTA): This is a primary technique for identifying the temperatures of phase transformations.[1][4] A sample is heated or cooled at a controlled rate alongside a thermally inert reference material. Phase transitions, which are endothermic or exothermic, are detected as temperature differences between the sample and the reference. These events correspond to liquidus, solidus, eutectic, and other transformation temperatures.[13]

3. Structural and Compositional Analysis:

-

X-ray Diffraction (XRD): XRD is essential for identifying the crystal structure of the phases present in an alloy at different temperatures.[4][12] By analyzing the diffraction patterns, the specific phases (e.g., η'', η', η) can be determined. High-temperature XRD allows for in-situ analysis of phases that are not stable at room temperature.[5][6]

-

Microscopy and Microanalysis:

-

Optical and Scanning Electron Microscopy (SEM): These methods are used to visualize the microstructure of the alloys, revealing the morphology, distribution, and relative amounts of the different phases.[4][5]

-

Electron Probe Microanalysis (EPMA): This technique provides quantitative chemical analysis of the individual phases observed in the microstructure, allowing for the precise determination of phase boundaries.[1][4]

-

Figure 2: Experimental workflow for phase diagram determination.

Phase Transformation Pathway: Cooling of a Cu-25at%Si Alloy

To illustrate the phase transformations, consider the cooling of an alloy with a composition of approximately Cu-25at%Si from the liquid state. This composition is close to the congruently melting η phase.

-

Above 859°C: The alloy is a homogeneous liquid (L).

-

At 859°C: The liquid begins to solidify directly into the high-temperature η phase. This is a congruent melting point, so the entire liquid transforms to η at this constant temperature.[1]

-

Between 859°C and ~620°C: The alloy consists entirely of the solid η phase.

-

At ~620°C: A polymorphic transformation begins, with the η phase transforming into the intermediate-temperature η' phase.[1]

-

Between ~620°C and ~570°C: The alloy consists of the solid η' phase.

-

At ~570°C: A second polymorphic transformation occurs as the η' phase transforms into the low-temperature η'' phase.[1]

-

Below ~570°C: The stable phase at room temperature is η''.

Figure 3: Cooling pathway for a near-stoichiometric Cu₃Si alloy.

References

- 1. New investigation of phase equilibria in the system Al–Cu–Si - PMC [pmc.ncbi.nlm.nih.gov]

- 2. researchgate.net [researchgate.net]

- 3. Cu-Si (Copper-Silicon) - ProQuest [proquest.com]

- 4. Experimental investigation of the Cu-Si phase diagram at x(Cu)>0.72 - PubMed [pubmed.ncbi.nlm.nih.gov]

- 5. researchgate.net [researchgate.net]

- 6. hasyweb.desy.de [hasyweb.desy.de]

- 7. researchgate.net [researchgate.net]

- 8. Eutectic, eutectoid, peritectoid, peritectic | PDF [slideshare.net]

- 9. rcet.org.in [rcet.org.in]

- 10. Eutectic system - Wikipedia [en.wikipedia.org]

- 11. Cu-Si (copper-silicon) - ProQuest [proquest.com]

- 12. jmmab.com [jmmab.com]

- 13. researchgate.net [researchgate.net]

An In-Depth Technical Guide to the Electronic Band Structure of Cu3Si

For Researchers, Scientists, and Drug Development Professionals

Abstract

This technical guide provides a comprehensive overview of the electronic band structure of copper silicide (Cu₃Si), a material of significant interest in various technological applications. This document synthesizes theoretical calculations and outlines the experimental methodologies used to investigate the electronic properties of this intermetallic compound. Key quantitative data are summarized, and detailed experimental and computational protocols are provided to facilitate further research. The metallic nature of Cu₃Si, characterized by the absence of a band gap, is a central feature of its electronic structure. This guide is intended for researchers and scientists seeking a thorough understanding of the electronic properties of Cu₃Si.

Introduction

Copper silicide (Cu₃Si) is an intermetallic compound that has garnered attention for its applications in microelectronics as a contact material and in catalysis.[1] A fundamental understanding of its electronic band structure is crucial for predicting and optimizing its performance in these roles. The arrangement of electron energy levels as a function of their momentum, known as the electronic band structure, dictates a material's electrical and optical properties. For Cu₃Si, both theoretical and experimental investigations are employed to elucidate these characteristics.

Crystal Structure of Cu₃Si

The electronic band structure is intrinsically linked to the crystal structure of a material. Cu₃Si can exist in several polymorphic forms, with the tetragonal structure (space group I4/mmm) being a commonly studied phase.[1] The crystallographic parameters for this phase are essential for theoretical calculations of the electronic band structure.

Theoretical Electronic Band Structure and Density of States

First-principles calculations based on Density Functional Theory (DFT) are a powerful tool for predicting the electronic structure of materials.[2]

Band Structure

The calculated band structure of tetragonal Cu₃Si reveals its metallic nature.[3] Multiple bands cross the Fermi level (E_F), which is the highest energy level that an electron can occupy at absolute zero temperature. This continuous distribution of energy states at the Fermi level allows for the easy excitation of electrons into conducting states, which is characteristic of metals. The absence of a band gap is a key feature, with the Materials Project database reporting a band gap of 0.000 eV.[1]

Density of States (DOS)

The Density of States (DOS) provides information about the number of available electronic states at each energy level. For Cu₃Si, the DOS at the Fermi level is non-zero, further confirming its metallic character.[3] The total DOS is a sum of the contributions from the constituent atoms, with the copper d-orbitals and silicon p-orbitals significantly contributing to the states near the Fermi level.

Quantitative Data

The following table summarizes the key quantitative data related to the electronic and structural properties of tetragonal Cu₃Si.

| Property | Value | Source |

| Crystal System | Tetragonal | Materials Project[1] |

| Space Group | I4/mmm | Materials Project[1] |

| Band Gap | 0.000 eV | Materials Project[1] |

| Character | Metallic | ResearchGate[3] |

Experimental and Theoretical Methodologies

A combination of experimental and theoretical methods is essential for a comprehensive understanding of the electronic band structure of Cu₃Si.

Experimental Protocol: Angle-Resolved Photoemission Spectroscopy (ARPES)

-

Sample Preparation: A single crystal of Cu₃Si is cleaved in situ under ultra-high vacuum (UHV) conditions to expose a clean, atomically flat surface.

-

Photon Source: A monochromatic light source, typically a synchrotron or a UV laser, is used to generate photons with a specific energy (e.g., 21.2 eV).[4]

-

Photoemission: The incident photons strike the sample surface, causing the emission of photoelectrons.

-

Electron Analyzer: A hemispherical electron analyzer measures the kinetic energy and emission angle of the photoemitted electrons.[5]

-

Data Acquisition: The intensity of the photoelectrons is recorded as a function of their kinetic energy and emission angle.

-

Data Analysis: The binding energy and crystal momentum of the electrons within the solid are determined from the measured kinetic energy and emission angle, allowing for the mapping of the band structure.

Theoretical Protocol: Density Functional Theory (DFT) Calculations

DFT calculations are a standard theoretical method for determining the electronic structure of materials. A typical workflow for calculating the electronic band structure of Cu₃Si is as follows:

-

Structure Definition: The crystal structure of tetragonal Cu₃Si (space group I4/mmm) is used as the input.[1]

-

Computational Method: The calculation is performed using a plane-wave basis set and pseudopotentials, as implemented in software packages like VASP or Quantum ESPRESSO.[6]

-

Exchange-Correlation Functional: The Generalized Gradient Approximation (GGA) with the Perdew-Burke-Ernzerhof (PBE) functional is a common choice for such calculations.[2][6]

-

Self-Consistent Field (SCF) Calculation: An initial SCF calculation is performed to determine the ground-state charge density. This involves setting parameters such as the plane-wave cutoff energy and the k-point mesh for Brillouin zone integration.

-

Band Structure Calculation: A non-self-consistent calculation is then performed along high-symmetry directions in the Brillouin zone to obtain the electronic band structure.

-

Density of States (DOS) Calculation: The DOS is calculated from the results of the SCF calculation, providing a distribution of electronic states as a function of energy.

Visualizations

Combined Workflow for Electronic Structure Determination

The following diagram illustrates a typical workflow for determining the electronic band structure of a material like Cu₃Si, integrating both theoretical and experimental approaches.

Caption: Workflow for Electronic Structure Determination.

Conclusion

References

- 1. researchgate.net [researchgate.net]

- 2. First-Principles study on the mechanical properties of Cu3Si compound | IEEE Conference Publication | IEEE Xplore [ieeexplore.ieee.org]

- 3. GitHub - afonari/emc: Effective Mass Calculator for Semiconductors [github.com]

- 4. Angle-resolved photoemission spectroscopy - Wikipedia [en.wikipedia.org]

- 5. Angle-resolved Photoemission Spectroscopy | Shen Laboratory [arpes.stanford.edu]

- 6. sites.chem.utoronto.ca [sites.chem.utoronto.ca]

Topic: Investigating the Cu-Si Reaction at Low Temperatures

An in-depth technical guide or whitepaper on the core.

Audience: Researchers, scientists, and drug development professionals.

Introduction

The solid-state reaction between copper (Cu) and silicon (Si) is of significant interest in microelectronics, particularly for interconnect metallization.[1] While high-temperature processes are well-documented, the reactions occurring at low temperatures—ranging from room temperature to a few hundred degrees Celsius—present unique phenomena and challenges. At these temperatures, the interaction is primarily governed by solid-state diffusion, leading to the formation of specific copper silicide phases. A remarkable aspect of this system is the catalytic oxidation of silicon at room temperature in the presence of copper silicide, a process that deviates significantly from conventional high-temperature silicon oxidation.[2][3][4]

This guide provides a comprehensive overview of the low-temperature Cu-Si reaction, focusing on phase formation, reaction kinetics, and thermodynamics. It details common experimental protocols used for investigation and presents key quantitative data to facilitate comparative analysis.

Low-Temperature Phase Formation

In the Cu-Si system, three equilibrium silicide phases are stable at low temperatures: η″-Cu₃Si, ε-Cu₁₅Si₄, and γ-Cu₅Si.[1] Experimental studies on both bulk and thin-film Cu/Si diffusion couples consistently show that the η″-Cu₃Si phase is the first to form during low-temperature annealing, typically around 200-230°C.[2][3][5] This phase remains the only one observed on bulk (100) Si.[4]

The sequence of phase formation as the reaction progresses or temperature increases is generally as follows: η″-Cu₃Si → ε-Cu₁₅Si₄ → γ-Cu₅Si.[1] The growth of these silicide layers is a diffusion-controlled process, with copper being the dominant diffusing species.[6]

dot

Caption: Sequential formation of low-temperature copper silicide phases.

Reaction Kinetics and Thermodynamics

The formation and growth of copper silicide at low temperatures are governed by diffusion mechanisms. The kinetics often follow a parabolic growth law (x² = k²t), indicating a diffusion-limited process.[7] The activation energy for the reaction varies depending on the diffusion pathway (bulk vs. grain boundary) and the nature of the silicon substrate (amorphous vs. crystalline).

Quantitative Data Summary

The following tables summarize key kinetic and thermodynamic data for the low-temperature Cu-Si reaction as reported in the literature.

Table 1: Activation Energies for Cu₃Si Formation

| System | Temperature Range (°C) | Diffusion Mechanism | Activation Energy (eV) | Reference |

|---|---|---|---|---|

| Cu / a-Si | 200 - 260 | - | 0.95 | [6] |

| Pure Cu / Si | > 470 | Bulk Diffusion | 1.75 | [6] |

| Pure Cu / Si | < 470 | Grain-Boundary Diffusion | 1.10 | [6] |

| P-doped Cu / Si | < 530 | Grain-Boundary Diffusion | 0.92 |[6] |

Table 2: Enthalpies of Formation for Copper Silicides

| Phase | Formation Reaction | Enthalpy of Formation (kJ/mol) | Reference |

|---|---|---|---|

| Cu₃Si | Cu + a-Si | -13.6 ± 0.3 | [7] |

| Cu₅Si | Cu + a-Si | -10.5 ± 0.6 | [7] |

| Cu₃Si | - | -24.4 (at RT) |[8][9] |

Special Case: Room-Temperature Oxidation of Silicon

A significant phenomenon in the Cu-Si system is the rapid, catalytic oxidation of silicon at room temperature in the presence of Cu₃Si.[2][4][10] While thermal oxidation of silicon typically requires temperatures above 700°C, the Cu₃Si phase acts as a catalyst, allowing a thick layer of silicon dioxide (SiO₂) to grow spontaneously underneath the silicide layer over several weeks in air.[2][3][4][10]

The mechanism involves Cu₃Si particles at the SiO₂/Si interface that catalyze the oxidation process.[2][3] This effect is so pronounced that SiO₂ layers exceeding one micrometer in thickness can form at room temperature.[2][4] The supply of oxygen is a controlling factor in this process.[10]

dot

Caption: Room-temperature catalytic oxidation of Si in the presence of Cu₃Si.

Experimental Protocols

Investigating the low-temperature Cu-Si reaction involves a multi-step process of sample preparation, controlled reaction induction, and material characterization.

Sample Preparation: Thin Film Deposition

Thin film diffusion couples are commonly used to study the Cu-Si reaction.

-

Substrate: Single-crystal silicon wafers, often (100) orientation, are typically used.[2][4] Amorphous silicon (a-Si) layers can also be used.[7]

-

Deposition Technique: Sputter deposition is a common method to prepare multilayered composites of Cu and Si with precise control over individual layer thicknesses, which can range from 2 to 100 nm.[6][7] Thermal evaporation is another technique used for depositing pure copper films.[11]

-

Controlled Atmosphere: Deposition is carried out in a high-vacuum environment to prevent contamination.

Reaction Induction: Low-Temperature Annealing

-

Method: Post-deposition annealing is performed to induce the solid-state reaction. This can be done in a conventional furnace or specialized systems like a Stacked Annealing Oven (SAO) for controlled, low-temperature thermal treatment.[12]

-

Atmosphere: Annealing is typically conducted in a controlled atmosphere, such as a vacuum (e.g., 10⁻⁸ Torr), nitrogen (N₂), or forming gas, to prevent oxidation of the copper film.[11][12]

-

Temperature Range: The temperature range for studying low-temperature reactions is typically from room temperature up to 500°C.[6][13] Isothermal annealing at specific temperatures (e.g., 200°C, 350°C, 450°C) is used to study the reaction progress over time.[5]

Characterization Techniques

A suite of analytical techniques is employed to characterize the resulting phases, reaction kinetics, and elemental distribution.

-

Differential Scanning Calorimetry (DSC): DSC is used to measure heat flow during annealing, allowing for the determination of reaction temperatures and enthalpies of formation.[7]

-

X-Ray Diffraction (XRD): XRD is essential for identifying the crystalline phases formed during the reaction, such as the different copper silicides.[5][6][7]

-

Transmission Electron Microscopy (TEM): TEM, including high-resolution (HRTEM) and cross-sectional TEM (XTEM), provides microstructural information, allows for the direct observation of interfacial layers, and can be used for in-situ heating experiments to observe the reaction in real-time.[13][14]

-

Rutherford Backscattering Spectrometry (RBS): RBS is used to analyze the elemental composition and depth profile of the thin films, revealing the extent of interdiffusion between Cu and Si.[2][5][11]

-

Auger Electron Spectroscopy (AES): AES is another surface-sensitive technique used to determine elemental composition and study interfacial reactions.[2][3]

dot

Caption: General experimental workflow for studying the Cu-Si reaction.

References

- 1. researchgate.net [researchgate.net]

- 2. pubs.aip.org [pubs.aip.org]

- 3. Formation of Cu3Si and its catalytic effect on silicon oxidation at room temperature for Journal of Vacuum Science and Technology A: Vacuum, Surfaces and Films - IBM Research [research.ibm.com]

- 4. dacemirror.sci-hub.se [dacemirror.sci-hub.se]

- 5. researchgate.net [researchgate.net]

- 6. researchgate.net [researchgate.net]

- 7. researchgate.net [researchgate.net]

- 8. Intermediate Cu-O-Si Phase in the Cu-SiO2/Si(111) System: Growth, Elemental, and Electrical Studies - PMC [pmc.ncbi.nlm.nih.gov]

- 9. pubs.acs.org [pubs.acs.org]

- 10. researchgate.net [researchgate.net]

- 11. pubs.aip.org [pubs.aip.org]

- 12. electrochem.org [electrochem.org]

- 13. Low temperature formation of copper rich silicides - Repository of the Academy's Library [real.mtak.hu]

- 14. researchgate.net [researchgate.net]

Spontaneous Formation of Copper Silicide Nanostructures: An In-depth Technical Guide

For Researchers, Scientists, and Drug Development Professionals

Abstract

The spontaneous formation of copper silicide nanostructures, driven by the reaction between copper and silicon sources, presents a fascinating and promising area of materials science. These nanoscale materials, including nanowires, nanorods, and thin films, exhibit unique electrical, mechanical, and catalytic properties, making them highly attractive for a range of applications, from microelectronics to energy storage and catalysis. This technical guide provides a comprehensive overview of the core principles and methodologies underlying the synthesis of these nanostructures. It delves into the primary formation mechanisms, including solid-state reactions, solvent-based growth, and chemical vapor deposition. Detailed experimental protocols for key synthesis techniques are provided, alongside a compilation of quantitative data summarizing the influence of various synthesis parameters on the resulting nanostructure characteristics. Furthermore, this guide employs visualizations to illustrate the intricate experimental workflows and reaction pathways, offering a deeper understanding of the spontaneous formation process.

Introduction

Copper silicides, intermetallic compounds of copper and silicon, have long been of interest in the semiconductor industry for their use in interconnects and contacts.[1] The formation of various copper silicide phases, such as copper-rich Cu₃Si and silicon-rich phases, is a well-documented phenomenon.[2] More recently, the ability to control the synthesis of these materials at the nanoscale has opened up new avenues for scientific exploration and technological innovation. The "spontaneous" nature of their formation, often driven by thermal annealing or solution-phase reactions, allows for the fabrication of complex nanostructures without the need for intricate lithographic patterning.[3]

This guide will explore the fundamental aspects of the spontaneous formation of copper silicide nanostructures, with a focus on providing practical information for researchers in the field.

Formation Mechanisms

The spontaneous formation of copper silicide nanostructures is primarily governed by three key mechanisms: solid-state reaction, solvent-based synthesis, and chemical vapor deposition (CVD).

Solid-State Reaction

This method involves the direct reaction between a solid copper source, typically a thin film, and a silicon substrate upon thermal annealing.[4] The process is driven by the diffusion of copper atoms into the silicon lattice, leading to the nucleation and growth of copper silicide phases.[5] The specific phase formed (e.g., Cu₃Si, Cu₁₅Si₄) and the morphology of the resulting nanostructures are highly dependent on factors such as the annealing temperature, time, and the orientation of the silicon substrate.[4][6]

Solvent-Based Synthesis

In this approach, a copper source (e.g., copper foil) is subjected to a high-boiling-point organic solvent containing a silicon precursor, such as phenylsilane.[3] At elevated temperatures, the silicon precursor decomposes, and the silicon atoms react with the copper surface to form copper silicide nanostructures, often in the form of high-density nanowire arrays.[7] This method offers excellent control over the dimensions and density of the resulting nanostructures.

Chemical Vapor Deposition (CVD)

CVD involves the introduction of volatile precursors of copper and silicon into a reaction chamber where they decompose and react on a substrate to form a thin film or nanostructures.[8] The growth can proceed through a Vapor-Liquid-Solid (VLS) or a Vapor-Solid-Solid (VSS) mechanism. In the VLS mechanism, a liquid metal catalyst droplet absorbs the precursors, and the nanostructure grows from the supersaturated droplet.[9][10] In the VSS mechanism, a solid catalyst facilitates the growth.[4] CVD allows for the synthesis of high-purity, single-crystalline nanowires.[11]

Data Presentation: Synthesis Parameters and Nanostructure Properties

The following tables summarize quantitative data from various studies on the synthesis of copper silicide nanostructures, highlighting the relationship between experimental parameters and the resulting material properties.

Table 1: Solid-State Reaction Parameters and Resulting Nanostructures

| Copper Film Thickness (Å) | Silicon Substrate | Annealing Temperature (°C) | Annealing Time | Resulting Silicide Phase | Nanostructure Morphology | Reference |

| 1000 | Si(100) | 600-750 | 30 min | Cu₃Si, Cu₄Si | Square and rectangular crystallites | [4] |

| 1000 | Si(111) | 750 | 30 min | Cu₃Si, Cu₄Si | Droplet-like crystallites | [4] |

| Not Specified | Si(100) | 200 | Not Specified | Not Specified | Formation rate ~5x faster than on Si(111) | [6] |

| 30 ± 2 | Si(100) with 4 ± 0.2 nm SiO₂ | Laser Annealing (6 ns pulses) | Not Specified | Cu₃Si | Periodic nanowires | [12] |

Table 2: Solvent-Based Synthesis of Copper Silicide Nanowires

| Copper Source | Silicon Precursor | Solvent | Reaction Temperature (°C) | Resulting Silicide Phase | Nanowire Dimensions | Reference |

| Copper Foil | Phenylsilane | High-boiling-point organic solvent | 460 | Cu₁₅Si₄ | High-density arrays, tight diameter spread | [3][7] |

Table 3: Chemical Vapor Deposition (CVD) for Copper Silicide Nanostructures

| Copper Precursor | Silicon Precursor | Substrate | Growth Temperature (°C) | Growth Mechanism | Resulting Silicide Phase | Nanostructure Morphology | Reference |

| Copper Powder | Si(100) wafer (source) | Au-colloid coated Si(100) | Not Specified | Vapor-Liquid-Solid (VLS) | Cu₃Si inclusions in Si nanowires | Nanowires | [13] |

| Butylsilane (BuSiH₃) | Copper foil | Copper foil | 570 | Not Specified | CuₓSi (3 < x < 5) | Nanoplatelets, nanowires, nanoribbons | [14] |

Table 4: Electrical Properties of Copper Silicide Nanostructures

| Silicide Phase | Nanostructure Type | Dimensions | Resistivity (μΩ·cm) | Reference | | :--- | :--- | :--- | :--- | :--- | :--- | | Cu₃Si | Nanowire | Not Specified | ~63 |[13] | | Cu₃Si | Nanowire | Not Specified | 206 |[15] | | Cu₃Si | Nanowire | Not Specified | < 30 |[3] |

Experimental Protocols

This section provides detailed methodologies for the key experiments cited in this guide.

Solid-State Reaction for the Formation of Cu₃Si Nanostructures

Objective: To synthesize copper silicide nanostructures via thermal annealing of a copper thin film on a silicon substrate.

Materials:

-

P-type Si(100) wafers

-

High-purity copper source for thermal evaporation

-

Deionized water

-

Hydrofluoric acid (HF), 10% solution

-

Nitrogen gas (high purity)

-

Vacuum thermal annealing furnace

Procedure:

-

Substrate Cleaning:

-

Cut Si(100) wafers into desired dimensions.

-

Clean the wafers ultrasonically in deionized water for 15 minutes.

-

Dip the wafers in a 10% HF solution for 1 minute to remove the native oxide layer.

-

Rinse the wafers thoroughly with deionized water and dry them with a stream of high-purity nitrogen gas.

-

-

Copper Film Deposition:

-

Immediately transfer the cleaned Si substrates into a high-vacuum thermal evaporation chamber.

-

Deposit a copper thin film of the desired thickness (e.g., 100 nm) onto the Si substrates. Maintain a low deposition rate to ensure film uniformity.

-

-

Thermal Annealing:

-

Place the Cu-coated Si substrates into a vacuum furnace.

-

Evacuate the furnace to a high vacuum.

-

Heat the substrates to the desired annealing temperature (e.g., 200-450 °C) at a controlled ramp rate.

-

Maintain the temperature for a specific duration (e.g., 30 minutes).

-

Cool the furnace down to room temperature under vacuum.

-

-

Characterization:

-

Analyze the morphology and crystal structure of the formed copper silicide nanostructures using Scanning Electron Microscopy (SEM) and X-ray Diffraction (XRD).

-

Solvent-Based Synthesis of Cu₁₅Si₄ Nanowires

Objective: To synthesize high-density arrays of Cu₁₅Si₄ nanowires on a copper foil.

Materials:

-

Copper foil (high purity)

-

Phenylsilane (Si precursor)

-

1-octadecene (high-boiling-point solvent)

-

Argon gas (high purity)

-

Three-neck flask

-

Heating mantle with temperature controller

-

Condenser

Procedure:

-

Reaction Setup:

-

Place a piece of copper foil into a three-neck flask.

-

Add 1-octadecene to the flask to cover the copper foil.

-

Connect a condenser to one neck of the flask and seal the other necks.

-

Purge the flask with argon gas for at least 30 minutes to create an inert atmosphere.

-

-

Synthesis:

-

Heat the flask to 460 °C using a heating mantle while stirring.

-

Once the temperature is stable, inject a specific amount of phenylsilane into the hot 1-octadecene.

-

Maintain the reaction at 460 °C for a set duration (e.g., 30-60 minutes).

-

-

Purification and Collection:

-

After the reaction, cool the flask to room temperature.

-

Remove the copper foil, which is now covered with copper silicide nanowires.

-

Wash the foil with an organic solvent (e.g., toluene or hexane) to remove any residual 1-octadecene.

-

Dry the sample under a stream of nitrogen.

-

-

Characterization:

-

Examine the morphology and density of the nanowires using SEM.

-

Determine the crystal phase of the nanowires using XRD and Transmission Electron Microscopy (TEM).

-

Visualization of Workflows and Mechanisms

The following diagrams, generated using the DOT language, illustrate the experimental workflows and the fundamental growth mechanism involved in the spontaneous formation of copper silicide nanostructures.

Caption: Experimental workflow for solid-state reaction synthesis.

Caption: Experimental workflow for solvent-based synthesis.

Caption: Schematic of the Vapor-Liquid-Solid (VLS) growth mechanism.

Conclusion

The spontaneous formation of copper silicide nanostructures offers a versatile and scalable approach to fabricating novel nanomaterials with significant technological potential. Understanding the underlying formation mechanisms and the influence of key synthesis parameters is crucial for controlling the morphology, crystal structure, and properties of these nanostructures. This technical guide has provided a detailed overview of the primary synthesis routes, compiled quantitative data to aid in experimental design, and presented clear experimental protocols. The visualizations of the workflows and growth mechanisms further enhance the understanding of these complex processes. Continued research in this area is expected to lead to further advancements in the controlled synthesis of copper silicide nanostructures and unlock their full potential in a wide range of applications.

References

- 1. apps.dtic.mil [apps.dtic.mil]

- 2. A robust and high performance copper silicide catalyst for electrochemical CO 2 reduction - Materials Advances (RSC Publishing) DOI:10.1039/D3MA00633F [pubs.rsc.org]

- 3. researchgate.net [researchgate.net]

- 4. researchgate.net [researchgate.net]

- 5. researchgate.net [researchgate.net]

- 6. researchgate.net [researchgate.net]

- 7. researchgate.net [researchgate.net]

- 8. "Synthesis of silicide nanomaterials using chemical vapour deposition m" by Hamid Norouzi Banis [ir.lib.uwo.ca]

- 9. researchgate.net [researchgate.net]

- 10. researchgate.net [researchgate.net]

- 11. A flexible chemical vapor deposition method to synthesize copper@carbon core–shell structured nanowires and the study of their structural electrical properties - New Journal of Chemistry (RSC Publishing) [pubs.rsc.org]

- 12. pubs.aip.org [pubs.aip.org]

- 13. researchgate.net [researchgate.net]

- 14. Controlled Synthesis of Copper-Silicide Nanostructures [ouci.dntb.gov.ua]

- 15. researchgate.net [researchgate.net]

Theoretical modeling of copper silicide interfaces

An in-depth technical guide on the theoretical modeling of copper silicide interfaces tailored for researchers, scientists, and drug development professionals.

Introduction

Copper silicide interfaces are of paramount importance in a variety of technological fields, most notably in microelectronics where they are integral to interconnects and contacts. The interaction between copper and silicon dictates the structural, electronic, and thermal properties of these interfaces, which in turn govern device performance and reliability. As device dimensions continue to shrink, a microscopic understanding of these interfaces becomes increasingly critical. Theoretical modeling, primarily through first-principles calculations, offers a powerful lens to investigate the atomic-scale phenomena that are often inaccessible to direct experimental observation.

This guide provides a comprehensive overview of the theoretical modeling of copper silicide interfaces. It details the primary computational methodologies, summarizes key quantitative data from theoretical and experimental studies, provides protocols for relevant experimental techniques, and explores the relevance of this research to the field of drug development, particularly in the areas of advanced biosensors, biocompatible materials, and catalysis.

Theoretical Modeling Methodologies

The theoretical investigation of copper silicide interfaces predominantly relies on atomistic simulation techniques that can accurately describe the quantum mechanical interactions between atoms.

Density Functional Theory (DFT)

Density Functional Theory (DFT) is the most widely used first-principles method for studying the properties of materials at the atomic scale. It is a quantum mechanical modeling method used to investigate the electronic structure of many-body systems. DFT is employed to calculate a wide range of properties for copper silicide interfaces, including:

-

Interface Energetics: Calculating the work of adhesion and interface formation energy to determine the stability of different interface configurations.

-

Electronic Structure: Determining the band alignment, Schottky barrier height, and density of states, which are crucial for understanding electrical transport across the interface.

-

Atomic Geometry: Optimizing the positions of atoms at the interface to find the lowest energy structure, revealing details about bond lengths, coordination, and interfacial reconstructions.

Molecular Dynamics (MD)

Molecular Dynamics simulations are used to study the time evolution of a system of atoms or molecules. While classical MD relies on empirical interatomic potentials, ab initio MD (AIMD) combines MD with DFT to provide a more accurate description of the atomic forces. For copper silicide interfaces, MD is used to investigate:

-

Interface Formation: Simulating the deposition of copper atoms onto a silicon surface to observe the initial stages of silicide formation.

-

Thermal Stability: Assessing the structural integrity and diffusion processes at the interface at elevated temperatures.

-

Mechanical Properties: Calculating stress-strain relationships to understand the mechanical response of the interface.

Key Interfacial Properties: A Quantitative Overview

The following tables summarize key quantitative data for copper silicide interfaces, derived from both theoretical calculations and experimental measurements.

Table 1: Theoretical Interfacial Properties of Copper Silicides

| Property | System/Phase | Value | Method |

| Adhesion Energy | Cu(001)/Si(001) | -0.138 eV/Ų | DFT |

| Adhesion Energy | Cu(111)/Si(111) | -0.137 eV/Ų | DFT |

| Adhesion Energy | Cu(110)/Si(110) | -0.110 eV/Ų | DFT |

| Work of Adhesion | Cu₃P/Cu (Si-doped) | 1.4273 J/m² | DFT |

| Interface Strength (Wsep) | a-Si/Graphene | 0.41 J/m² | DFT |

| Structural Parameters | |||

| Phase | η''-Cu₃Si | Tetragonal, I4/mmm | DFT |

| Cu-Cu Bond Length | η''-Cu₃Si | 2.55 Å, 2.58 Å | DFT |

| Cu-Si Bond Length | η''-Cu₃Si | 2.55 Å, 2.58 Å | DFT |

Table 2: Experimental Electronic Properties of Copper/Silicon Interfaces

| Property | System | Value | Measurement Technique |

| Schottky Barrier Height | Cu / n-type Si | 0.52 ± 0.02 eV | Hot-electron spectroscopy |

| Schottky Barrier Height | Cu / n-type Si | ~0.6 eV | I-V, C-V measurements |

| Schottky Barrier Height | Cu / p-type Si | ~0.5 eV | I-V, C-V measurements |

Experimental Protocols

Theoretical models are validated and informed by experimental data. The following are detailed protocols for two key techniques used to fabricate and characterize copper silicide thin films.

Protocol 1: Physical Vapor Deposition (PVD) of Copper on Silicon

Physical Vapor Deposition is a common technique for depositing thin films of copper onto silicon substrates. Sputtering is a widely used PVD method.

-

Substrate Preparation:

-

Begin with a p-type Si(100) wafer.

-

Perform a standard cleaning procedure to remove organic and inorganic contaminants. This typically involves sequential ultrasonic baths in acetone, isopropyl alcohol, and deionized water.

-

To remove the native oxide layer, dip the substrate in a dilute hydrofluoric acid (HF) solution (e.g., 2% HF) for 60 seconds, followed by a final rinse in deionized water and drying with nitrogen gas.

-

-

Chamber Preparation and Pumping:

-

Mount the cleaned Si substrate onto the substrate holder in the sputtering chamber.

-

Evacuate the chamber to a base pressure of at least 10⁻⁶ Torr to minimize contamination from residual gases.

-

-

Deposition Process:

-

Introduce a high-purity inert gas, typically Argon (Ar), into the chamber, raising the pressure to a working pressure in the range of 1-20 mTorr.

-

Apply a high DC voltage to the copper target (cathode) to ignite and sustain an Ar plasma.

-

The Ar ions are accelerated towards the target, ejecting copper atoms through momentum transfer.

-

The sputtered copper atoms travel through the vacuum and deposit onto the silicon substrate.

-

The substrate temperature is a critical parameter and is typically maintained in the range of 50°C to 400°C, depending on the desired film properties.[1][2]

-

A typical deposition rate is on the order of 1 nm/s.[3]

-

-

Post-Deposition Annealing (Optional):

-

To form copper silicide, the as-deposited Cu/Si structure is annealed in a vacuum or inert atmosphere.

-

Annealing temperatures between 200°C and 500°C are typically used to promote the formation of various copper silicide phases, with η''-Cu₃Si being a common phase formed at lower temperatures.

-

Protocol 2: X-ray Diffraction (XRD) Analysis of Copper Silicide Films

XRD is a primary technique for identifying the crystalline phases present in the thin film.

-

Instrument Setup:

-

Use a diffractometer equipped with a Cu Kα radiation source (λ = 1.5406 Å).

-

For thin film analysis, a grazing incidence XRD (GIXRD) setup or a standard Bragg-Brentano configuration with parallel beam optics is often preferred to enhance the signal from the film and reduce substrate diffraction.

-

-

Sample Mounting:

-

Mount the copper silicide/Si sample on the sample stage, ensuring it is flat and at the correct height relative to the X-ray beam.

-

-

Scan Parameters:

-

Perform a 2θ/ω scan over a range that covers the expected diffraction peaks for copper, silicon, and various copper silicide phases. A typical range is 20° to 80° in 2θ.

-

Set the step size to a value such as 0.02°.

-

The scan speed (or dwell time per step) should be chosen to achieve a good signal-to-noise ratio; a rate of 1-4°/min is common.[4]

-

-

Data Analysis:

-

The resulting diffractogram will show peaks (reflections) at specific 2θ angles.

-

Identify the crystalline phases present by comparing the peak positions and relative intensities to standard diffraction patterns from a database such as the Joint Committee on Powder Diffraction Standards (JCPDS).

-

The peak broadening can be analyzed using the Scherrer equation to estimate the average crystallite size in the film.

-

Visualizations of Workflows and Relationships

References

An In-depth Technical Guide to the Magnetic Properties of Copper Silicide Alloys

Affiliation: Google Research

Abstract

This technical guide provides a comprehensive overview of the magnetic properties of binary copper silicide (Cu-Si) alloys. Primarily, these materials are characterized by their diamagnetic nature, a consequence of their electronic structure. This document details the theoretical basis for this behavior, summarizes the qualitative magnetic character, and outlines the sophisticated experimental protocols required for the characterization of such weakly magnetic materials. While direct quantitative data for specific copper silicide phases is scarce in publicly accessible literature, this guide establishes a foundational understanding for researchers. Furthermore, it presents standardized workflows for the synthesis and magnetic analysis of these alloys. This work is intended for researchers, materials scientists, and professionals in fields where the precise magnetic characterization of metallic alloys is critical. The connection to drug development is speculative and would likely involve novel applications of weakly magnetic materials, a frontier not yet substantially explored in existing research.

Introduction to Copper Silicide Alloys

Copper silicide refers to a range of intermetallic compounds formed between copper and silicon. Common phases include Cu₅Si and Cu₃Si, among others, which form based on the specific stoichiometry and thermodynamic conditions during synthesis[1]. These alloys are recognized for their applications in microelectronics, where they are used to passivate copper interconnects, serving as diffusion barriers and suppressing electromigration[1].

From a magnetic standpoint, materials are broadly classified based on their response to an applied magnetic field. This response is quantified by the magnetic susceptibility (χ), which is the ratio of the induced magnetization in the material to the applied magnetic field intensity[2].

-

Diamagnetic Materials (χ < 0): These materials are weakly repelled by a magnetic field. This effect arises from the orbital motion of electrons, creating small current loops that oppose the external field. Most materials with paired electrons, including elemental copper in its bulk metallic form, exhibit diamagnetism[2].

-

Paramagnetic Materials (χ > 0): These materials are weakly attracted to a magnetic field. This behavior is due to the presence of unpaired electrons, whose magnetic moments align with the external field[2].

-

Ferromagnetic Materials (χ >> 0): These materials exhibit strong attraction to magnetic fields and can retain magnetization after the field is removed.

Based on the electronic configuration of bulk copper, which features a filled 3d electron shell, and silicon, a metalloid, copper silicide alloys are predicted to be predominantly diamagnetic[1]. Any significant paramagnetic or ferromagnetic behavior in these alloys would likely stem from impurities or specific nanostructural effects that are not characteristic of the bulk material.

Magnetic Character of Copper Silicide

There is a notable scarcity of specific quantitative data in peer-reviewed literature for the magnetic susceptibility of binary copper silicide alloys such as Cu₅Si. However, based on the known properties of constituent elements and related compounds, a strong inference can be made. Both elemental copper and silicon are diamagnetic in their bulk, crystalline forms[1]. Theoretical studies on similar transition-metal silicides, such as NiSi thin films, have predicted them to be nonmagnetic[3][4]. Therefore, it is the established consensus that binary copper silicide alloys are weakly diamagnetic materials.

An important consideration is the potential for an anomalous paramagnetic "Curie tail" at very low temperatures, which has been observed in high-purity elemental copper. This phenomenon is attributed to intrinsic electronic excitations rather than impurities[5]. It is plausible that similar subtle effects could be present in copper silicide alloys at cryogenic temperatures, superimposed on the dominant diamagnetic response.

Data on Magnetic Properties

| Alloy Phase (e.g., Cu₅Si) | Synthesis Method | Measurement Temperature (K) | Magnetic Susceptibility (χ) (unitless SI) | Molar Susceptibility (χₘ) (m³/mol) | Classification | Reference |

| Data Not Available | Diamagnetic (Expected) | |||||

| Data Not Available | Diamagnetic (Expected) |

Experimental Protocols

The characterization of weakly magnetic materials like copper silicides requires highly sensitive instrumentation. The two primary methods for such measurements are the Gouy balance and the Superconducting Quantum Interference Device (SQUID) magnetometer.

Synthesis of Copper Silicide Alloys

A typical method for producing polycrystalline copper silicide samples for magnetic analysis is through arc melting or solid-state reaction.

-

Material Preparation: High-purity copper (e.g., 99.99%) and silicon powders or granules are weighed in the desired stoichiometric ratio (e.g., 5:1 for Cu₅Si).

-

Mixing: The constituent materials are thoroughly mixed.

-

Arc Melting: The mixture is placed in a water-cooled copper hearth within an arc furnace. The chamber is evacuated and purged with an inert gas (e.g., Argon). A high current is passed through a tungsten electrode to strike an arc, melting and alloying the materials. The resulting ingot is flipped and re-melted several times to ensure homogeneity.

-

Annealing: The as-cast alloy is often sealed in an evacuated quartz tube and annealed at an elevated temperature (e.g., 600-800 °C) for an extended period (days to weeks) to promote phase equilibrium and grain growth.

-

Sample Preparation: The annealed ingot is cut or powdered into a suitable shape for magnetic measurement, such as a long, cylindrical rod for a Gouy balance.

Magnetic Susceptibility Measurement: Gouy Balance

The Gouy method is a classic and accessible technique for measuring the magnetic susceptibility of solid and liquid samples.

Principle: The method measures the apparent change in the mass of a sample when it is suspended in a region with a magnetic field gradient. A diamagnetic sample will be pushed out of the field, resulting in an apparent loss of weight, while a paramagnetic sample is pulled in, causing an apparent increase in weight.

Protocol:

-

Sample Preparation: The solid copper silicide alloy is shaped into a uniform, long cylinder or packed uniformly into a cylindrical sample tube of known cross-sectional area (A).

-

Initial Weighing: The sample is suspended from a sensitive analytical balance such that its lower end is positioned in the center of the pole gap of a strong electromagnet, while the upper end is in a region of negligible field strength. The mass is recorded with the magnetic field off (mₐ).

-

Magnetic Field Application: The electromagnet is turned on to produce a strong, uniform magnetic field (H).

-

Final Weighing: The new apparent mass of the sample is recorded with the magnetic field on (mₑ).

-

Calculation: The volume susceptibility (κ) is calculated using the formula: F = (mₑ - mₐ)g = ½ * (κ - κ₀) * A * H² where g is the acceleration due to gravity, and κ₀ is the volume susceptibility of the surrounding air (often negligible).

Magnetic Susceptibility Measurement: SQUID Magnetometer

For the highest sensitivity, particularly for very weakly diamagnetic materials or for studying temperature-dependent effects, a SQUID magnetometer is the instrument of choice.

Principle: A SQUID is an extremely sensitive detector of magnetic flux, based on superconducting loops containing Josephson junctions. When a sample is moved through a superconducting detection coil, it induces a tiny current proportional to the sample's magnetic moment. The SQUID measures the magnetic field generated by this current.

Protocol:

-

Sample Mounting: A small, precisely weighed sample of the copper silicide alloy is mounted in a sample holder (typically a plastic straw to minimize background signal).

-

System Cooldown: The SQUID system is cooled with liquid helium to achieve a superconducting state (typically operating at temperatures from 1.9 K to 400 K).

-

Measurement Sequence: The sample is moved through a set of superconducting pickup coils in the presence of a highly uniform, applied DC magnetic field.

-

Data Acquisition: The SQUID sensor measures the change in magnetic flux, which is converted into the magnetic moment of the sample.

-

Data Analysis:

-

M vs. H Curve: To confirm diamagnetism, the magnetic moment (M) is measured as a function of the applied field (H) at a constant temperature. For a diamagnetic material, this will be a straight line with a negative slope.

-

M vs. T Curve: To investigate temperature-dependent effects (like a potential Curie tail), the magnetic moment is measured at a constant applied field while varying the temperature.

-

Visualized Workflows and Relationships

Experimental Workflow

The following diagram illustrates the general workflow for the synthesis and characterization of copper silicide alloys.

Caption: Workflow for alloy synthesis and magnetic property analysis.

Logical Relationship of Properties

The magnetic properties of copper silicide are intrinsically linked to its electronic structure, which in turn is determined by its composition and crystal structure.

Caption: Determinants of magnetic properties in Cu-Si alloys.

Conclusion and Future Outlook

Copper silicide alloys are fundamentally diamagnetic materials due to their electronic structure, characterized by paired electrons in filled d-bands. While this property is well-established from a theoretical standpoint, there is a clear gap in the experimental literature providing specific quantitative magnetic susceptibility values for defined Cu-Si phases. The advanced experimental protocols detailed herein, particularly SQUID magnetometry, provide the necessary framework for future research to fill this gap. Such data would be invaluable for materials scientists working on applications where even weak magnetic responses are significant. The relevance to drug development remains speculative and would require the development of novel applications where diamagnetic materials could play a role, for instance, in modulating magnetic fields in highly sensitive diagnostic equipment or as non-interfering components in targeted delivery systems. Future work should focus on the precise measurement of the magnetic properties of well-characterized, high-purity copper silicide phases.

References

- 1. Magnetic susceptibility for the Cu2-II-IV-S4 (II=Mn, Fe; IV=Si, Ge or Sn) compounds: Exchange interaction parameters [ve.scielo.org]

- 2. Magnetic susceptibility - Wikipedia [en.wikipedia.org]

- 3. researchgate.net [researchgate.net]

- 4. discovery.researcher.life [discovery.researcher.life]

- 5. arxiv.org [arxiv.org]

The Untapped Potential of Doped Copper Silicide: A Technical Guide to a New Frontier in Thermoelectrics

Authored for: Researchers, Scientists, and Drug Development Professionals December 17, 2025

Executive Summary

The quest for efficient, cost-effective, and environmentally benign thermoelectric materials is a cornerstone of modern materials science, with profound implications for waste heat recovery and solid-state cooling. While significant research has focused on materials like bismuth telluride, lead telluride, and various silicides such as those based on magnesium (Mg₂Si), manganese (MnSi₁.₇₃), and cobalt (CoSi), copper silicide (CuₓSi) remains a largely unexplored candidate. This technical guide consolidates the current understanding of thermoelectric principles through the lens of well-studied analogous materials to project the thermoelectric potential of doped copper silicide. By examining doping strategies in other metal silicides and copper chalcogenides, we provide a foundational framework for future research, detailing robust experimental protocols for synthesis and characterization, and presenting a theoretical case for the investigation of this promising material class.

Introduction: The Case for Copper Silicide

Copper silicide, typically found in phases like Cu₃Si and Cu₅Si, is recognized for its excellent electrical and thermal conductivity.[1][2] While these properties are advantageous in microelectronics for applications like interconnects[3], they are traditionally viewed as counterproductive for thermoelectric applications, where a low thermal conductivity is paramount. However, the field of thermoelectrics has demonstrated that material properties can be dramatically tuned through strategic doping and nanostructuring.

The primary figure of merit (ZT) for a thermoelectric material is given by ZT = (S²σT)/κ, where S is the Seebeck coefficient, σ is the electrical conductivity, T is the absolute temperature, and κ is the thermal conductivity.[4] The central challenge is to decouple these interdependent parameters—typically, increasing electrical conductivity (σ) also increases the electronic contribution to thermal conductivity (κₑ), while the Seebeck coefficient often decreases.

This guide posits that the metallic or semi-metallic nature of copper silicide presents a unique starting point. If doping can introduce favorable band structure modifications to enhance the Seebeck coefficient while simultaneously introducing phonon scattering mechanisms to reduce lattice thermal conductivity (κₗ), doped copper silicide could emerge as a viable thermoelectric material. Lessons from analogous systems, such as Al-doped CoSi[5][6] and various doped copper chalcogenides[7][8], suggest that such a strategy is feasible.

Doping Strategies: Lessons from Analogous Systems

Given the limited direct research on doped copper silicide for thermoelectric applications, we turn to more mature material systems to infer potential outcomes.

Insights from Other Thermoelectric Silicides

Transition metal silicides like Mg₂Si and Higher Manganese Silicides (HMS) are prominent eco-friendly thermoelectric materials.[4] Doping is the primary method used to optimize their carrier concentration and enhance performance.

-

N-type Doping (e.g., Bi, Sb in Mg₂Si): Bismuth and Antimony are effective n-type dopants for Mg₂Si, donating electrons and increasing the carrier concentration. This boosts electrical conductivity, and while it reduces the Seebeck coefficient, an optimal balance can be found to maximize the power factor (S²σ).[1] A peak ZT of ~1.0 has been achieved in Bi-doped Mg₂Si.[1]

-

P-type Doping (e.g., Al, Ge in HMS): Aluminum and Germanium are used to tune the properties of p-type HMS. Co-doping strategies have been shown to simultaneously improve the power factor and reduce thermal conductivity, leading to ZT values approaching unity.[9]

-

Aliovalent Substitution (e.g., Al in CoSi): Substituting trivalent Al for tetravalent Si in CoSi introduces holes. Studies on CoSi₁₋ₓAlₓ show that this substitution significantly alters the transport properties. While it was found to decrease the overall ZT in CoSi by negatively impacting electrical properties, it effectively lowered thermal conductivity through point defect scattering.[5][6] This highlights the critical role of the host material's band structure in determining the outcome of a doping strategy.

For copper silicide, a similar approach of substituting Si with elements from Group 13 (B, Al, Ga) or Group 15 (P, As, Sb) could be a primary strategy to introduce p-type or n-type behavior, respectively.

Insights from Copper Chalcogenides (Cu₂X, X=S, Se, Te)

Copper chalcogenides, particularly Cu₂Se, are renowned for their high ZT values, reaching up to 2.62 in Al-doped samples.[7][10] Their success provides crucial clues for manipulating a copper-based lattice.

-

Cation Site Doping (e.g., Li, Na, Mg, Al in Cu₂Se): Doping at the copper site with alkali metals (Li, Na) or Group 2 and 13 elements (Mg, Al) has proven highly effective. These dopants can optimize the hole concentration, leading to a significant enhancement of the Seebeck coefficient and power factor.[7][8]

-

Anion Site Doping (e.g., S in Cu₂Se): Introducing sulfur into the selenium lattice of Cu₂Se creates additional phonon scattering centers, which effectively reduces lattice thermal conductivity. This strategy, combined with an optimized power factor, has led to ZT values as high as 2.0.[8]

These results suggest that for copper silicide, doping on the Cu site with elements like Li, Na, or Mg, or creating Cu-deficient structures, could be a powerful lever for enhancing thermoelectric performance.

Quantitative Data from Analogous Doped Systems

To provide a quantitative basis for the potential of doped copper silicide, the following tables summarize the thermoelectric properties of select analogous materials. This data serves as a benchmark for what could be achievable.

Table 1: Thermoelectric Properties of Al-Doped Cobalt Silicide (CoSi₁₋ₓAlₓ) at 300 K

| Dopant Conc. (x) | Electrical Resistivity (ρ) (µΩ·m) | Seebeck Coefficient (S) (µV/K) | Thermal Conductivity (κ) (W/m·K) | Figure of Merit (ZT) | Reference |

| 0 | 1.5 | -85 | 10.5 | ~0.015 | [5][6] |

| 0.01 | 4.0 | -60 | 8.0 | ~0.003 | [5][6] |

| 0.04 | 12.0 | -20 | 6.5 | <0.001 | [5][6] |

| 0.08 | 15.0 | +10 | 6.0 | <0.001 | [5][6] |

Data extracted from graphical representations in the cited literature and is approximate.

Table 2: High-Temperature Thermoelectric Properties of Doped Copper Selenide (Cu₂Se)

| Dopant | Max. ZT | Temperature (K) | Key Enhancement Mechanism | Reference |

| None (Pure Cu₂Se) | ~1.5 | 1000 | Intrinsic liquid-like Cu ions | [7] |

| Al | 2.62 | 1029 | Optimized carrier concentration | [7][10] |

| Li (Cu₁.₉₈Li₀.₀₂Se) | 2.14 | 973 | Reduced hole concentration, phonon scattering | [7] |

| Na (Cu₁.₉₆Na₀.₀₄Se) | 2.1 | 973 | Reduced hole concentration, phonon scattering | [8] |

| Mg | 1.6 | 860 | Reinforced electrical conductivity | [8] |

| S (Cu₂Se₀.₉S₀.₁) | 2.0 | 1000 | Enhanced phonon scattering | [8] |

Table 3: Thermoelectric Properties of Doped Higher Manganese Silicide (HMS)

| Material System | Dopant(s) | Max. ZT | Temperature (K) | Key Enhancement Mechanism | Reference | | :--- | :--- | :--- | :--- | :--- | | HMS | Undoped | ~0.4 | 700-800 | Intrinsic properties |[1] | | HMS | Al, Ge | ~0.6-0.8 | 800-850 | Optimized carrier concentration |[1][4] | | HMS | Nb | 0.46 | 773 | Increased power factor, reduced thermal conductivity |[11] |

Experimental Protocols

The successful synthesis and accurate characterization of novel thermoelectric materials are critical. The following sections detail standardized protocols applicable to the study of doped copper silicides, compiled from best practices in the field.[12][13]

Synthesis of Doped Copper Silicide

A common and effective method for producing bulk polycrystalline silicides is through solid-state reaction followed by consolidation.

Protocol: Solid-State Reaction and Spark Plasma Sintering (SPS)

-

Precursor Selection: Start with high-purity elemental powders of copper, silicon, and the desired dopant(s) (e.g., Al, Mg, Sb).

-

Stoichiometric Mixing: Accurately weigh the elemental powders according to the target stoichiometry (e.g., (Cu₁₋ₓMgₓ)₃Si).

-

Mechanical Alloying: Load the mixed powders into a hardened steel or tungsten carbide vial along with grinding media inside an argon-filled glovebox to prevent oxidation. Perform high-energy ball milling for 5-20 hours to achieve a nanostructured, homogeneous alloyed powder.

-

Consolidation: Transfer the resulting powder into a graphite die. Load the die into a Spark Plasma Sintering (SPS) machine.

-

Sintering Parameters: Heat the sample to a sintering temperature between 700°C and 900°C under a uniaxial pressure of 50-80 MPa in a vacuum or inert atmosphere. A rapid heating rate (50-100°C/min) and a short dwell time (5-15 minutes) are typical.

-

Sample Recovery: After cooling, extract the densified pellet from the die and polish its surfaces to remove any graphite contamination for subsequent characterization.

Thermoelectric Property Characterization

Accurate measurement of S, σ, and κ is essential for determining ZT.

Protocol: Seebeck Coefficient and Electrical Conductivity Measurement

-

Sample Preparation: Cut a bar-shaped sample (e.g., 2x2x10 mm³) from the sintered pellet.

-

Apparatus: Use a commercial system (e.g., Linseis LSR-3, ZEM-3) or a custom-built setup. The standard method is a four-probe configuration.

-

Measurement Principle:

-

Electrical Conductivity (σ): A constant DC current (I) is passed through the two outer probes. The voltage drop (V) across the two inner probes, separated by a known distance (L), is measured. The resistance R = V/I and conductivity σ = L/(R·A), where A is the sample's cross-sectional area.

-

Seebeck Coefficient (S): A small temperature gradient (ΔT) is established across the inner probes by a heater at one end of the sample. The resulting thermoelectric voltage (ΔV) is measured across the same inner probes. The Seebeck coefficient is calculated as S = -ΔV/ΔT.

-

-

Procedure: Perform measurements at discrete temperature points from room temperature up to the target operating temperature (e.g., 800 K) under a high vacuum or inert gas to prevent sample degradation.

Protocol: Thermal Conductivity Measurement

-

Sample Preparation: Cut a thin, disc-shaped sample (e.g., 10 mm diameter, 1-2 mm thickness) from the sintered pellet. Coat both faces with a thin layer of graphite to ensure uniform emissivity and absorption.

-

Apparatus: The laser flash analysis (LFA) method is the standard technique (e.g., Netzsch LFA 457).

-

Measurement Principle: The front face of the sample is irradiated with a short, high-intensity laser pulse. An infrared detector measures the temperature rise on the rear face as a function of time. The thermal diffusivity (α) is calculated from the time it takes for the rear face to reach half its maximum temperature rise.

-

Calculation of Thermal Conductivity (κ): The thermal conductivity is calculated using the equation κ = α · ρ_d · C_p, where:

-

α is the measured thermal diffusivity.

-

ρ_d is the density of the sample (measured by the Archimedes method).

-

C_p is the specific heat capacity (can be estimated using the Dulong-Petit law or measured via Differential Scanning Calorimetry, DSC).

-

-

Procedure: Conduct LFA measurements over the desired temperature range.

Protocol: Hall Effect Measurement

To understand the electronic transport properties, Hall measurements are used to determine carrier type, carrier concentration (n), and carrier mobility (µ).

-

Sample Preparation: A square-shaped sample (van der Pauw geometry) or a Hall bar geometry is prepared. Four electrical contacts are made at the corners or in the specified configuration.

-

Apparatus: A physical property measurement system (PPMS) or a dedicated Hall effect measurement system is used, which includes a controllable magnet, a current source, and a voltmeter.

-

Procedure:

-

A known current (I) is passed through two adjacent contacts, and the voltage (V) is measured across the other two.

-

A magnetic field (B) is applied perpendicular to the sample plane.

-

The Hall voltage (V_H) is measured as the change in transverse voltage with and without the magnetic field.

-

The carrier concentration (n) is calculated using n = (I · B) / (q · t · V_H), where q is the elementary charge and t is the sample thickness.

-

The Hall mobility (µ) is calculated from µ = R_H · σ, where R_H is the Hall coefficient (R_H = V_H · t / (I · B)).

-

Projected Pathways to High Performance

Based on the analysis of analogous systems, we can chart a logical path for optimizing the thermoelectric properties of copper silicide.

Conclusion and Future Outlook

While direct experimental evidence for high thermoelectric performance in doped copper silicide is currently lacking in the scientific literature, a comprehensive analysis of analogous material systems provides a compelling case for its investigation. The strategies that have yielded significant gains in other silicides and copper chalcogenides—namely, carrier concentration tuning via aliovalent substitution and thermal conductivity reduction through point defect scattering—are directly applicable to the Cu-Si system.

The path forward requires a systematic exploration of various p-type and n-type dopants. Initial candidates could include Al, Ga, and B for p-type, and Sb, P, and As for n-type doping on the Si site, as well as Li, Na, and Mg on the Cu site. The synthesis and characterization protocols detailed in this guide provide a robust framework for undertaking this research. The combination of low-cost, earth-abundant constituent elements and the potential for property tuning makes doped copper silicide a dark horse in the race for next-generation thermoelectric materials, warranting dedicated research efforts to unlock its full potential.

References

- 1. spintronics.cmshom.co.kr [spintronics.cmshom.co.kr]

- 2. Seebeck coefficient - Wikipedia [en.wikipedia.org]

- 3. researchgate.net [researchgate.net]

- 4. academic.oup.com [academic.oup.com]

- 5. scispace.com [scispace.com]

- 6. researchgate.net [researchgate.net]

- 7. Doping Effect on Cu2Se Thermoelectric Performance: A Review - PMC [pmc.ncbi.nlm.nih.gov]

- 8. mdpi.com [mdpi.com]

- 9. researchgate.net [researchgate.net]

- 10. researchgate.net [researchgate.net]

- 11. Enhancing thermoelectric performance of higher manganese silicide through Nb incorporation | springerprofessional.de [springerprofessional.de]

- 12. researchgate.net [researchgate.net]

- 13. researchgate.net [researchgate.net]

Methodological & Application